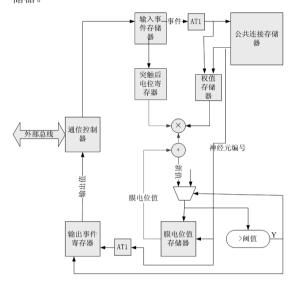

器以及相关附属器件。PN 处理单元的工作流程是: 当外部有输入数据通过总线进入 PN 处理器时先存放在输入事件存储器; 系统根据事件时间将数据输入到突触后电势寄存器; 同时输入值被编号后分别放入公共连接存储器; 突触后电势 PSP 值与其他神经元的权值相乘后与原有膜电位值相加, 相加结果更新膜电位存储器值; 同时结果与阈值相比较, 如果大于阈值则将结果输出到输出存储器中作为该神经元的输出结果存放在输出时间存储器。

图 3 PN 处理单元工作原理图

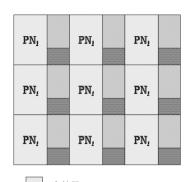

| $R_{PN_1}$ | $R_{pN_1}$ | $R_{pN_1}$ |

|------------|------------|------------|

| $R_{pN_1}$ | $R_{PN_1}$ | $R_{pN_1}$ |

| $R_{PN_1}$ | $R_{pN_1}$ | $R_{pN_1}$ |

图 4 人工神经网络系统逻辑图

系统是由若干个神经元处理器构成。如图 4 所示,人工神经网络系统由若干个神经元共同构成,图 5 表示了人工神经网络的硬件构成。每一个人工神经网络都是由若干个神经元处理单元构成,每个神经元处理单元又是由逻辑运算器、存储器和通信单元构成。将这些神经元处理器构建在一块电路板或者芯片上,同时处理器与处理器通过总线连接起来相互通信,共同完成神经网络的运算。系统还为每一个神经元单位配置了一个 PN 处理器,处理器之间相互独立,并行计算。当外部刺激(输入)进入系统时,立刻被分配到各个 PN 处理器并行计算

本文以 Gerstner 的尖峰神经元 模型为基础,设计

存储器 逻辑运算单元 通信接口

图 5 人工神经网络系统硬件结构图

了模拟神经元工作的 PN 处理单元,并由若干个 PN 处理单元构成模拟人类神经系统的人工神经网络的硬件系统。相对于在传统计算机上的操作,PN 处理单元的并行性使新系统有更强的处理能力,有效地提高了神经网络的计算速度,使神经网络系统有更好的应用前景。

(作者单位:广东肇庆科技职业技术学院)

## 参考文献:

[1]Gerstner, W. & Kistler, W.M. Spiking neuron models:single neurons, populations, plasticity. Cambridge, UK: Cambridge University Press, 2002.

[2]Mazad S. Zaveri. Dan Hammerstrom1. Performance/price estimates for cortex-scale hardware: A design space exploration, 2011, (24).

[3]徐明华,甘强.脉冲神经网络的振荡与分割[J].生物物理学报,1997,(1).

[4]夏克文.神经网络设计及其电路实现[J].石油仪器,1994,(3).

[5]黄远灿,孙圣和,韩京清.基于 Lagrange 乘子法的 非线性规划神经网络[J].电子学报,1998,(1).

责任编辑 何丽华